一、Multisim 11.0 核心功能与升级亮点(官方发布重点)

(一)首发核心突破(2010 年 1 月官方发布版)

- 原理图网表系统重构:彻底重新架构原理图捕捉环境,新增页内连接器(On-page Connector)和全局连接器(Global Connector),无需绘制实际导线即可实现电路连接,解决传统布线杂乱、节点命名混乱的问题,让电路图更清晰、更稳定,减少布线错误与文件损坏概率 [4]。

- 器件库大幅扩充:在 10.0 版本基础上,新增 2000 + 来自亚诺德半导体、美国国家半导体、NXP、飞利浦等主流厂商的真实器件模型,包含新的机电模型、AC/DC 电源转换器和开关模式电源模型,同时新增 90 + 引脚精确的连接器,方便 NI 硬件自定义附件设计,器件参数均基于真实 datasheet,仿真结果更精准。

- 混合仿真能力强化:优化 SPICE 3F5 仿真引擎,提升模拟、数字、射频电路的协同仿真效率,解决射频与基带信号融合仿真的瓶颈,新增 AC 单频分析功能,可精准评估射频电路的频率响应,适配无线通信、射频识别(RFID)等场景 [8]。

- FPGA 与 MCU 仿真支持:首次新增可编程逻辑设计(FPGA/PLD/CPLD)仿真功能,支持从原理图进行 FPGA 设计,同时支持 MCU 仿真,可通过汇编语言和 C 语言为单片机注入程序,填补了 10.0 版本在可编程逻辑仿真领域的空白 [7]。

- 仿真分析与建模优化:升级 SPICE 建模能力,支持直接查看 SPICE 网表,新增器件电流与功率分析功能,可在仿真过程中实时监测器件工作状态;优化蒙特卡洛分析、温度扫描等高级分析工具,提升复杂电路的可靠性评估能力 [11]。

(二)11.0.2 补丁版关键升级(2010 年 7 月发布)

- 优化连接器功能,提升页内 / 全局连接器的稳定性,解决连接异常问题,同时新增从元件向导直接放置元件的功能,提升设计效率。

- 强化与 Ultiboard 11 的协同设计,优化正向 / 反向标注功能,确保原理图与 PCB 版图的网表同步更新,减少设计偏差 [12]。

- 提升软件加载与保存性能,修复大文件仿真卡顿、崩溃的 Bug,优化虚拟仪器显示效果,解决部分仪器波形乱码问题。

- 更新器件数据库,补充新增厂商的器件模型,修复部分器件参数错误,增强仿真精度;新增模型加密功能,保护自定义器件模型安全。

(三)全版本通用核心能力

- 图形化电路设计:提供直观的拖拽式电路捕捉环境,支持元件自动连线、节点命名、参数快速编辑,内置 4500 + 基础元件库,支持自定义元件创建,适配从简单电阻电路到复杂系统级设计的全流程。

- 20 + 虚拟仪器集成:包含示波器、函数发生器、万用表、频谱分析仪、逻辑分析仪、网络分析仪等 20 种虚拟仪器,支持多仪器并行测量,数据实时显示并可导出至 Excel 进行后处理,模拟真实实验室测试环境,降低硬件测试成本。

- 18 种专业分析功能:覆盖直流工作点、直流扫描、交流小信号、瞬态、傅里叶、噪声、失真、参数扫描、蒙特卡洛、温度扫描等 18 种分析类型,提供从电路静态偏置到动态特性的全面评估,满足工程设计与教学验证需求。

- 协同设计能力:与 Ultiboard 11 无缝集成,可直接将仿真验证后的原理图导出为 PCB 版图,支持元件封装匹配、网表同步更新,形成从设计到制板的完整工作流,提升开发效率。

- 教育适配功能:内置电子教材、实验指导、电路示例库,支持教师创建自定义实验,学生可通过交互式仿真理解电路原理,适配电子工程、自动化、通信等专业的教学需求,是高校实验室的标准教学工具。

二、NI Multisim 11.0安装教程

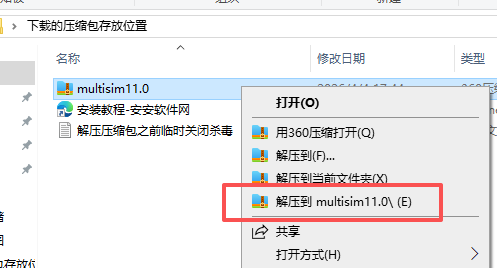

- 下载好压缩包,右键解压

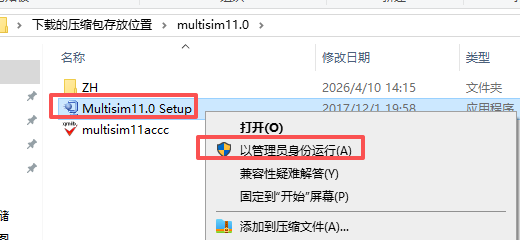

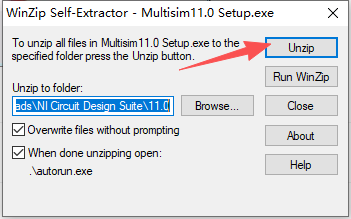

- 右键如图运行

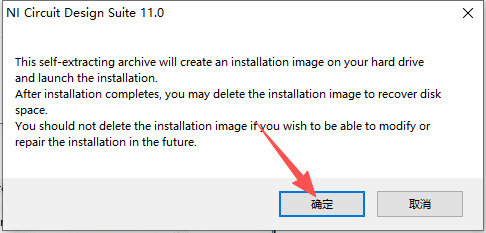

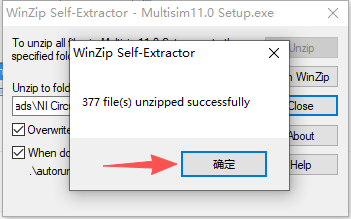

- 确定

- 点击unzip

- 确定

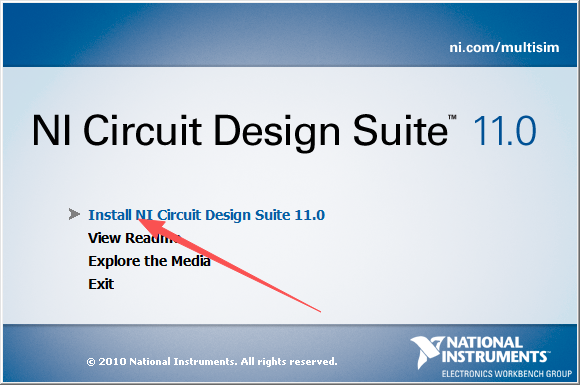

- 点击第一个

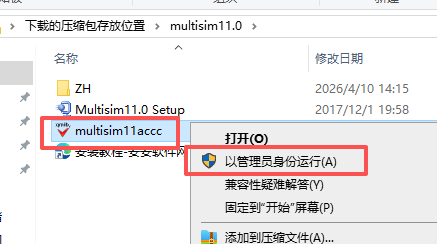

- 返回到解压的文件夹如图运行

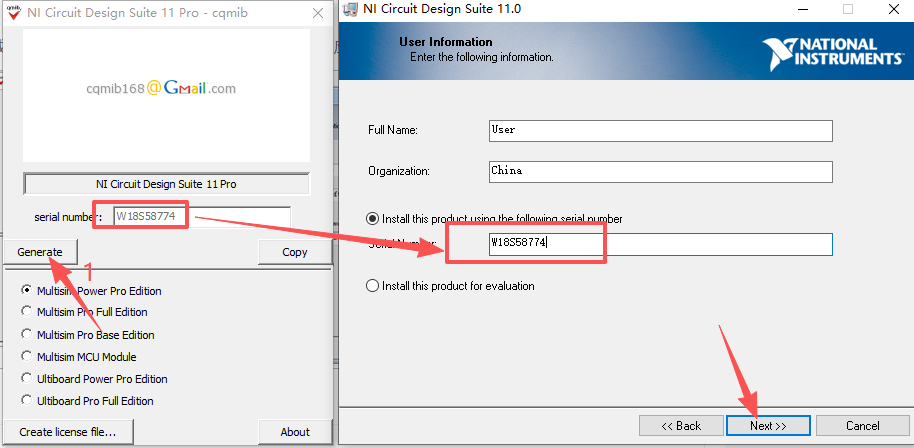

- 点击G开头如图描述复制粘贴

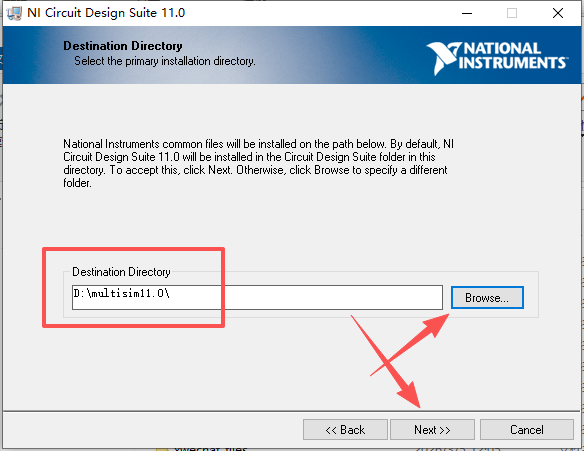

- 选择安装位置

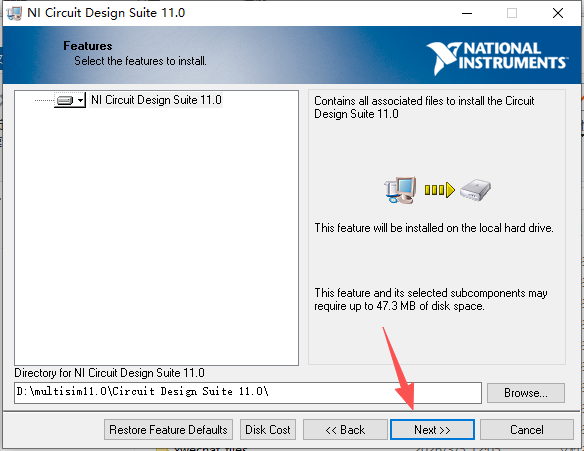

- 点击next

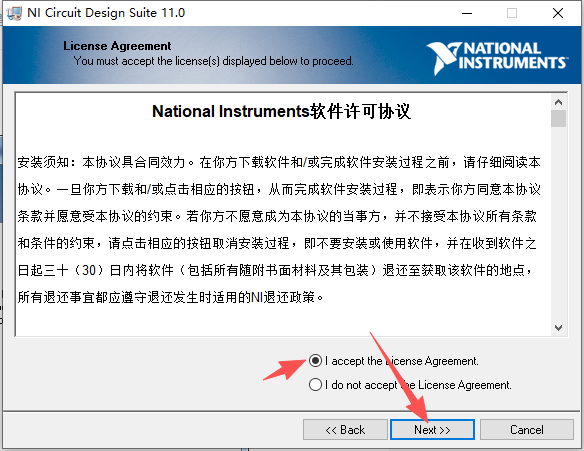

- 点击next

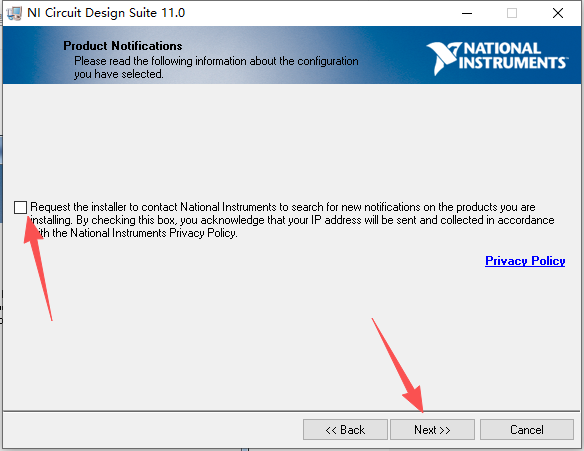

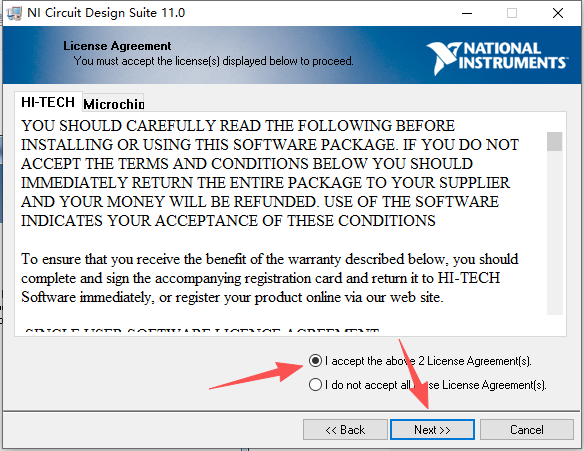

- 继续

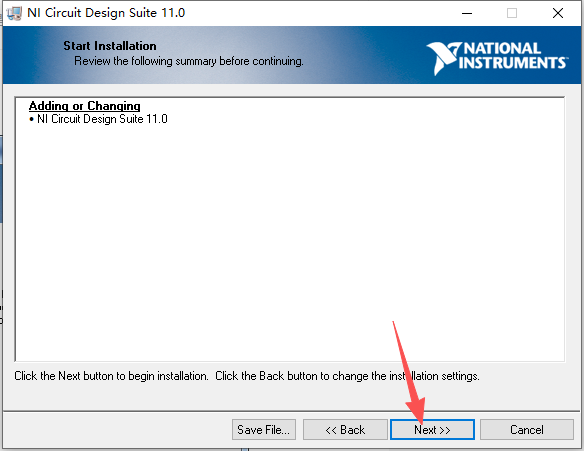

- 继续

- 继续

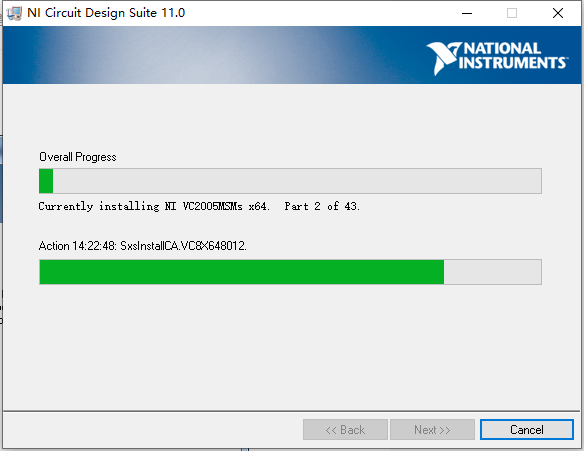

- 等待安装

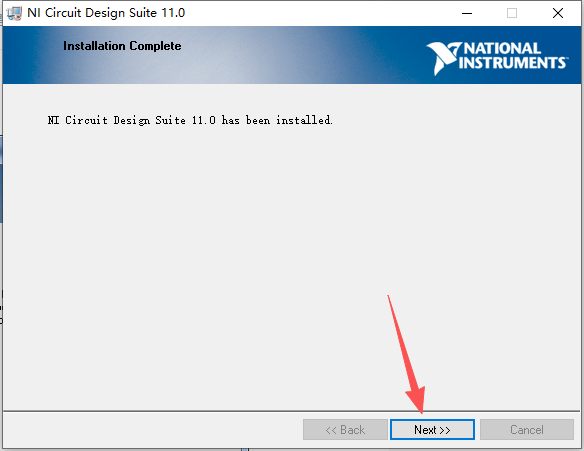

- 点击next

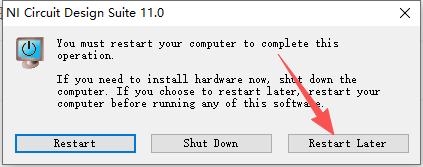

- 点击第三个

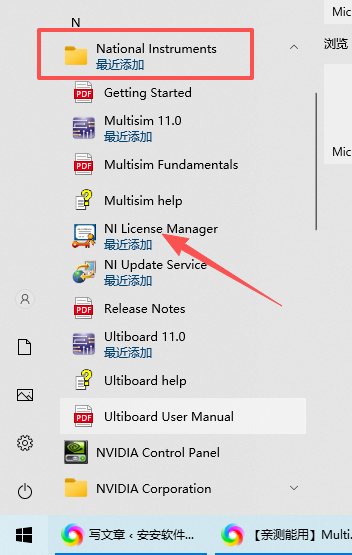

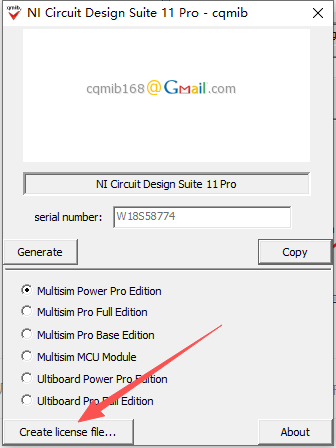

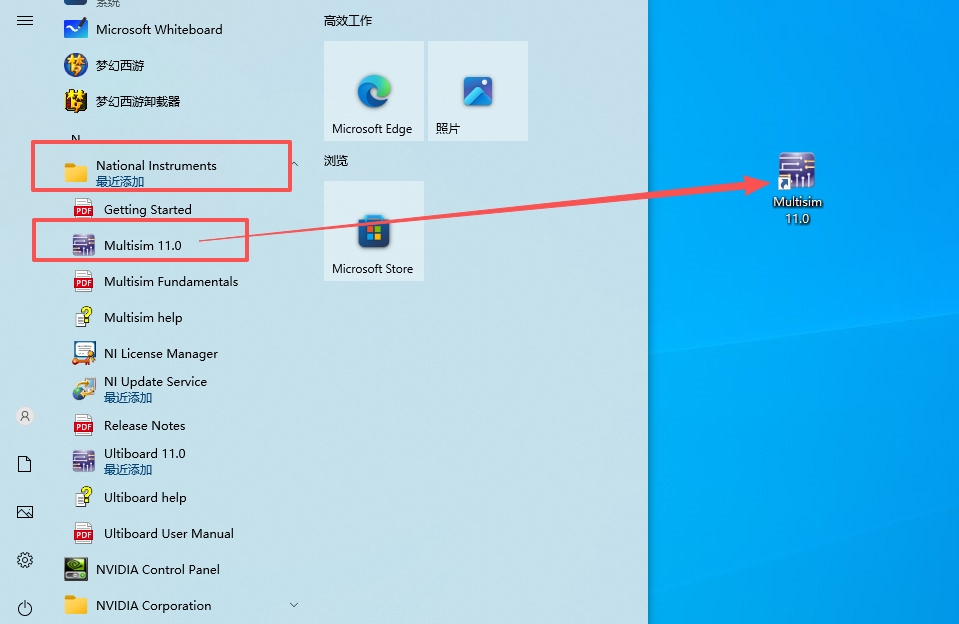

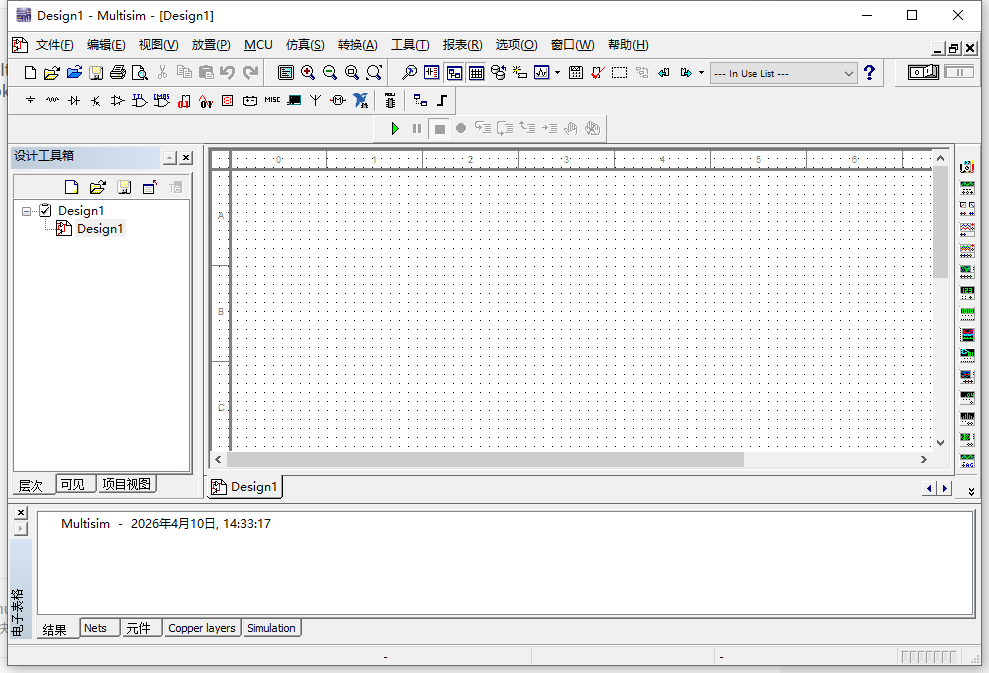

- 点击开始菜单,打开如图

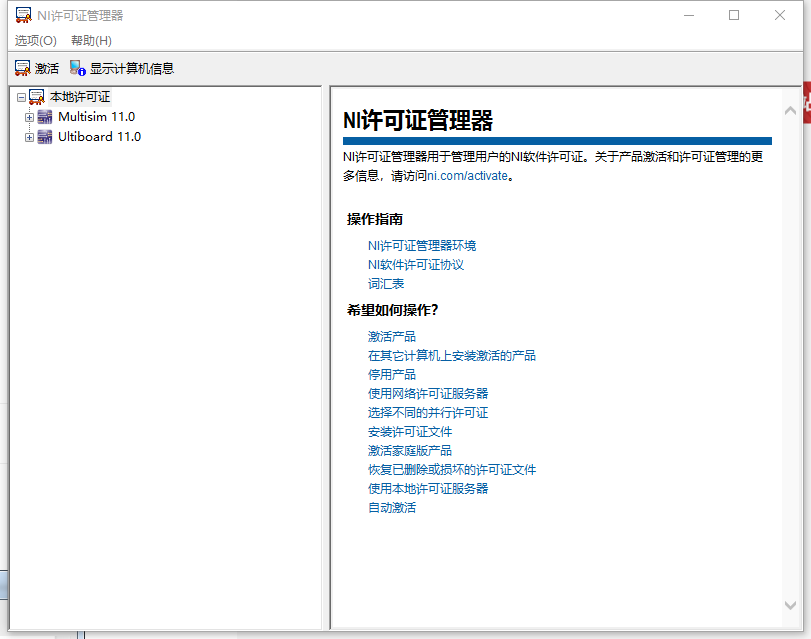

- 不要关闭

- 点击左下角

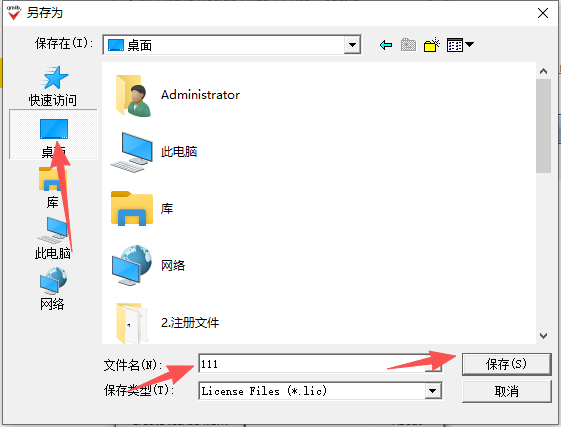

- 存到桌面

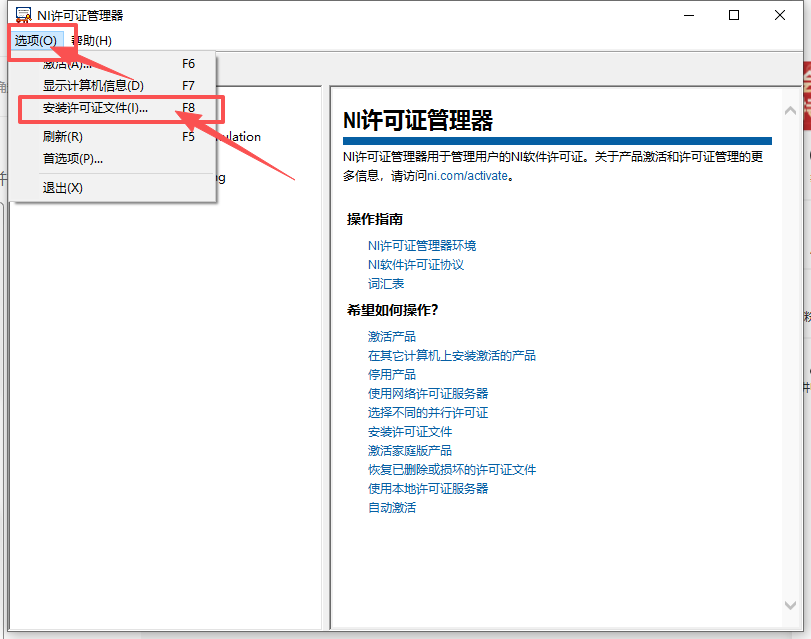

- 如图点击

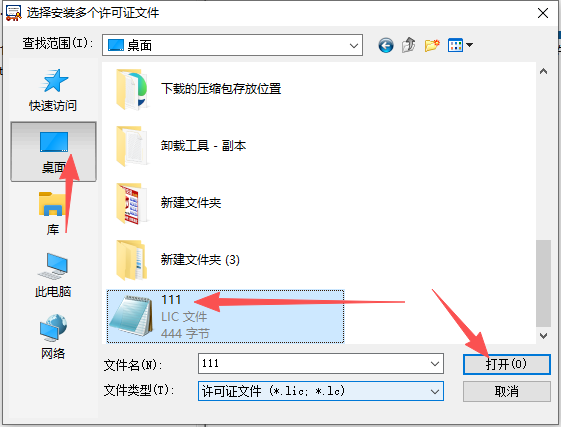

- 到桌面打开

- 拖拽到桌面

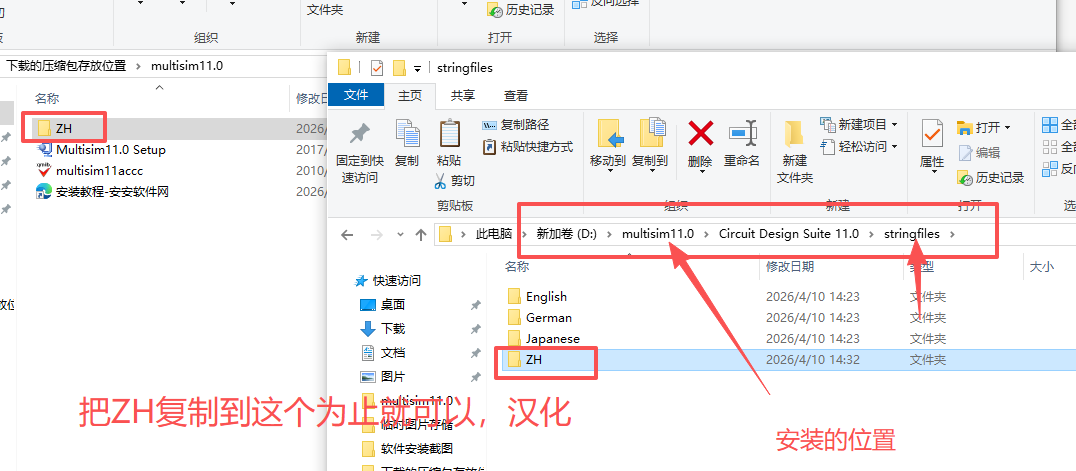

- 如图描述

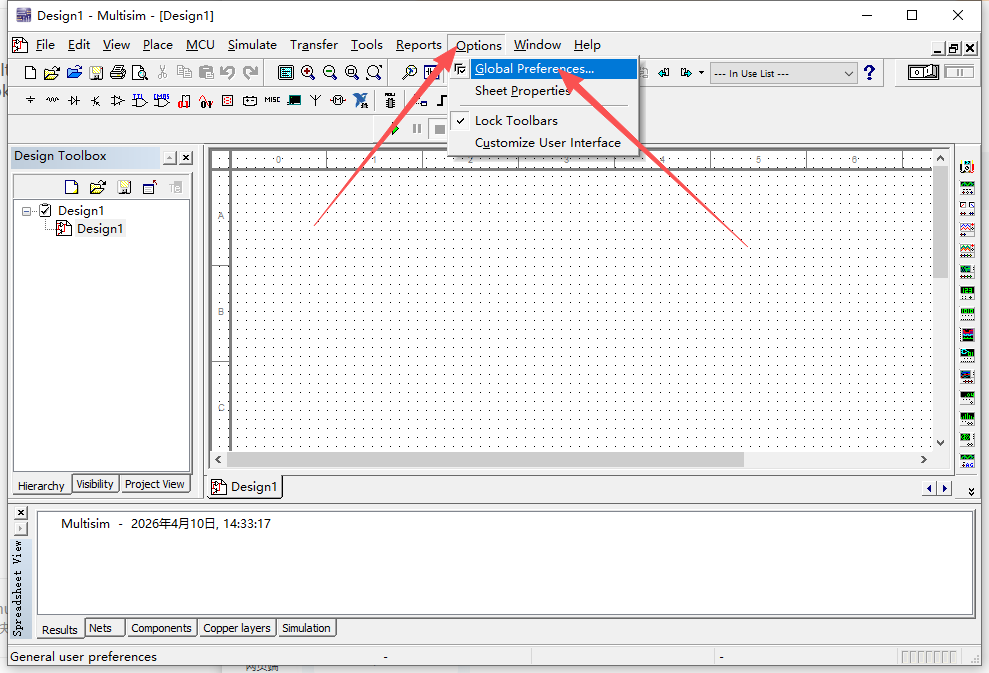

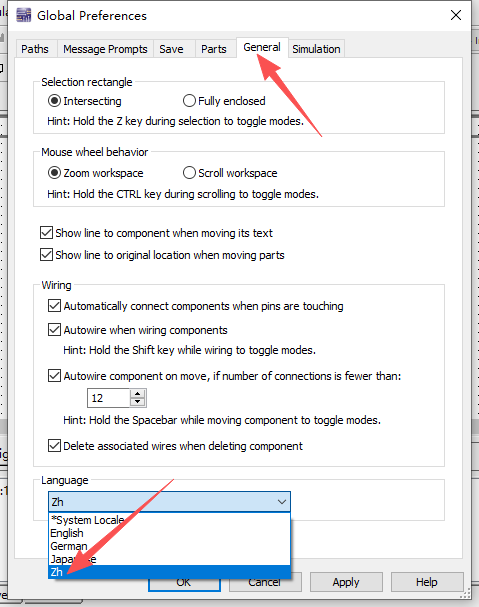

- 设置中文

三、系统配置要求(官方标准,适配 Multisim11.0,无冗余)

最低配置(满足基础电路仿真,适配教学场景)

| 配置项 | 要求 |

|---|---|

| 操作系统 | Windows XP SP2 / Windows Vista / Windows 7(32 位 / 64 位) |

| 处理器 | Intel Pentium 4 / AMD Athlon 2.0GHz 及以上,支持 SSE2 指令集 |

| 运行内存 | 1GB(基础电路仿真),建议 2GB 及以上 |

| 硬盘空间 | 5GB 可用空间,预留 2GB 缓存空间(建议使用机械硬盘即可满足基础需求) |

| 显卡 | 支持 DirectX 9.0c,128MB 显存,1024×768 分辨率及以上 |

| 其他 | .NET Framework 2.0 及以上,IE 6.0 及以上浏览器 |

推荐配置(满足复杂电路 / 射频 / FPGA 仿真,适配工程设计)

| 配置项 | 要求 |

|---|---|

| 操作系统 | Windows 7 64 位(兼容性最佳) |

| 处理器 | Intel Core 2 Duo / AMD Phenom II 3.0GHz 及以上,四核优先 |

| 运行内存 | 4GB(复杂电路 / 射频仿真),建议 8GB 及以上 |

| 硬盘空间 | 10GB SSD 可用空间,提升仿真数据读写速度(大型电路仿真刚需) |

| 显卡 | NVIDIA GeForce 9600GT / AMD Radeon HD 4670 及以上,512MB 显存 |

| 其他 | .NET Framework 3.5 SP1,IE 8.0 及以上,支持多显示器(方便多仪器并行操作) |

补充说明

- 不支持 macOS 系统,仅适配 Windows 平台;Windows 8 及以上系统可兼容安装,但部分旧版虚拟仪器可能存在显示异常,建议优先使用 Windows 7 系统。

- 射频仿真、FPGA 仿真、蒙特卡洛分析等高级功能建议使用推荐配置,可大幅提升仿真速度与稳定性,避免卡顿、崩溃。

- 无需安装额外插件,安装包自带完整器件库与虚拟仪器,补丁更新后可直接使用所有核心功能。

四、完整官方快捷键(分行 无简化,适配 Multisim11.0,含新增功能快捷键)

基础文件操作快捷键

Ctrl+O:打开现有电路文件

Ctrl+S:快速保存当前文件

Ctrl+Shift+S:文件另存为

Ctrl+P:打印当前电路原理图

Ctrl+W:关闭当前电路文件

Ctrl+Q:退出 Multisim 软件

F1:打开帮助文档

Ctrl+K:打开首选项设置面板

Ctrl+Shift+P:打开项目打包功能(11.0 新增)

元件操作快捷键

Ctrl+Q:放置导线(Wire)

Ctrl+R:旋转选中元件(90 度顺时针)

Ctrl+Shift+R:旋转选中元件(90 度逆时针)

Ctrl+F:翻转选中元件(水平)

Ctrl+Shift+F:翻转选中元件(垂直)

Delete:删除选中元件 / 导线

Ctrl+X:剪切选中内容

Ctrl+C:复制选中内容

Ctrl+V:粘贴内容

Ctrl+A:全选电路内容

Ctrl+Z:撤销上一步操作

Ctrl+Y:重做 / 向前恢复操作

Ctrl+Shift+H:将选中电路转换为层次模块(Hierarchical Block)

Ctrl+Shift+S:将选中电路转换为子电路(Subcircuit)

视图控制快捷键

Ctrl+-:缩小视图

Ctrl+0:视图适配窗口大小

Ctrl+1:视图 100% 实际大小显示

空格键:临时切换为抓手工具平移视图

F2:显示 / 隐藏栅格

F3:显示 / 隐藏页面边界

F4:显示 / 隐藏元件引脚编号

F5:显示 / 隐藏节点名称

F6:显示 / 隐藏导线名称

F7:显示 / 隐藏元件数值

F8:显示 / 隐藏元件参考标识

仿真与分析快捷键

F10:暂停 / 继续仿真

Ctrl+E:打开元件参数编辑窗口

Ctrl+B:打开仿真分析设置面板

Ctrl+L:打开电路列表窗口

Ctrl+M:打开测量探针窗口

Ctrl+T:打开 SPICE 网表生成窗口(11.0 优化)

Ctrl+Shift+B:打开批次仿真设置面板

Ctrl+Shift+E:打开 AC 单频分析设置(11.0 新增)

虚拟仪器快捷键

Ctrl+Shift+I:显示 / 隐藏所有已放置仪器

Alt+1:打开示波器(Oscilloscope)

Alt+2:打开函数发生器(Function Generator)

Alt+3:打开万用表(Multimeter)

Alt+4:打开频谱分析仪(Spectrum Analyzer)

Alt+5:打开逻辑分析仪(Logic Analyzer)

Alt+6:打开网络分析仪(Network Analyzer)

11.0 新增功能专属快捷键

Ctrl+Shift+G:放置全局连接器(11.0 新增)

Ctrl+Shift+F:打开 FPGA 仿真设置面板(11.0 新增)

Ctrl+Shift+D:打开器件电流 / 功率监测窗口(11.0 新增)

五、常见问题及解决方法(针对性 Multisim11.0,含补丁版适配问题)

- 仿真运行后无结果,提示 “网表生成错误”

解决方法:

- 检查电路是否使用了新增的页内 / 全局连接器,确保连接器命名唯一,无重复节点

- 确认所有元件均有对应的 SPICE 模型,删除无模型的自定义元件,重新选择器件库中的标准元件

- 打开 “视图→SPICE 网表”,查看网表错误提示,修复布线错误、节点未连接问题

- 升级至 11.0.2 补丁版,修复网表生成的已知 Bug,提升网表稳定性

- 器件库无法加载、部分新增器件找不到

解决方法:

- 确认安装时已完整安装器件库组件,未安装可重新运行安装程序选择 “修复”,勾选 “完整器件库”

- 检查器件库路径设置,在首选项中确认库文件路径正确,未被修改或移动

- 使用元件搜索功能(Ctrl+Shift+F),输入新增器件的厂商名称或型号(如 NXP、AC/DC 转换器),精准查找

- 手动加载补丁版新增的器件库,将补丁包中的库文件复制到软件安装目录的 “libraries” 文件夹下

- FPGA 仿真失败,提示 “可编程逻辑模块加载异常”

解决方法:

- 确认选中的 FPGA 器件型号支持仿真,部分高端 FPGA 型号仅支持 PCB 设计,不支持仿真

- 检查 FPGA 原理图连接是否正确,确保电源、接地、输入输出引脚连接无误

- 关闭其他占用大量系统内存的程序,FPGA 仿真对内存要求较高,建议内存不低于 4GB

- 重新安装 FPGA 仿真组件,运行安装程序选择 “修复”,勾选 “可编程逻辑仿真模块”

- 虚拟仪器显示乱码、波形卡顿

解决方法:

- 确认系统区域设置为中文(中国),非 Unicode 程序语言设置为中文,避免字符编码异常

- 更新显卡驱动到最新稳定版本,关闭显卡节能模式,启用硬件加速

- 升级至 11.0.2 补丁版,修复虚拟仪器显示 Bug,优化波形渲染速度

- 降低虚拟仪器采样频率,减少数据量,避免卡顿

- 无法导出原理图至 Ultiboard 11 进行 PCB 设计

解决方法:

- 确认已安装配套的 Ultiboard 11 软件,版本与 Multisim11.0 完全兼容(不可混用其他版本)

- 检查原理图中所有元件均有对应的 PCB 封装,无封装元件无法导出,可手动为元件指定封装

- 导出前运行电路规则检查(ERC),修复所有布线错误、节点冲突后再导出

- 优化正向标注设置,在 “工具→标注→正向标注” 中确认参数正确,确保网表同步

- 软件启动缓慢、大文件仿真卡顿

解决方法:

- 关闭不必要的后台程序,释放系统内存,建议内存不低于 4GB,复杂仿真建议 8GB 及以上

- 清理临时文件,删除 C 盘 Multisim 缓存目录下的冗余文件,将暂存盘设置为空间充足的磁盘

- 降低视图显示质量,关闭动画效果、阴影显示等非必要功能,提升操作流畅度

- 禁用自动备份功能,在首选项中调整备份频率或关闭自动备份,减少资源占用

六、实操应用落地案例(适配 Multisim11.0 新增功能,贴合教学与工程场景)

6.1 实操一:使用新增连接器搭建多级放大电路(11.0 专属)

- 新建 Multisim 电路文件,从元件库中选择 NPN 晶体管(2N3904)、电阻、电容、12V 直流电源和 1kHz 正弦波信号源,同时添加页内连接器(Ctrl+Shift+J)和全局连接器(Ctrl+Shift+G)。

- 搭建两级共射极放大电路,使用页内连接器连接两级电路的输入 / 输出端,避免布线杂乱;使用全局连接器连接电源和接地,确保所有模块供电稳定。

- 放置示波器、万用表,示波器通道 1 测量输入信号,通道 2 测量输出信号,万用表测量两级晶体管的静态工作点。

- 运行直流工作点分析,确认两级晶体管均工作在放大区,调整基极电阻使静态电流符合设计要求。

- 运行瞬态分析,观察示波器波形,测量放大倍数,验证连接器连接的稳定性,确保两级电路信号传输正常。

- 优化电路参数,调整集电极电阻和发射极电阻,提升放大倍数和带宽,完成多级放大电路设计,保存工程文件。

6.2 实操二:RC 低通滤波器仿真验证(适配 11.0 分析功能)

- 新建电路文件,选择电阻(1kΩ)、电容(1μF)、函数发生器(10Hz-100kHz 正弦波)、示波器和波特图仪,搭建 RC 低通滤波器(电阻与电容串联,输入接电阻端,输出接电容端)。

- 参数计算:根据公式 f_c=1/(2πRC) 计算截止频率约为 159Hz,理论上低于截止频率信号衰减小于 3dB,高于截止频率信号衰减大于 3dB。

- 仿真分析(11.0 新增功能应用):

- 瞬态分析:输入 100Hz 和 200Hz 正弦波,观察输出波形幅度变化,验证低频信号衰减小、高频信号衰减大的特性

- AC 单频分析(Ctrl+Shift+E):设置不同频率点,精准测量各频率下的信号衰减,与理论值对比

- 参数扫描分析:改变电阻值(500Ω-2kΩ),观察截止频率变化,验证 RC 参数对滤波特性的影响

- 数据导出:将仿真数据导出至 Excel,绘制幅频特性曲线,与理论曲线对比,误差控制在 5% 以内,验证设计正确性。

6.3 实操三:FPGA 简单逻辑电路仿真(11.0 新增功能)

- 新建电路文件,从 FPGA 器件库中选择基础 FPGA 芯片,添加开关、LED 指示灯、5V 直流电源和限流电阻,搭建简单的逻辑控制电路(实现开关控制 LED 点亮 / 熄灭)。

- 通过 “工具→FPGA 仿真设置”,配置 FPGA 仿真参数,选择仿真模式,导入简单的逻辑控制程序(汇编语言或 C 语言)。

- 放置逻辑分析仪,捕获输入(开关)和输出(LED)的时序波形,确认逻辑功能正确性。

- 运行仿真,测试不同开关状态下 LED 的点亮情况,验证 FPGA 逻辑控制的稳定性。

- 故障排查:故意断开 FPGA 电源,观察 LED 状态变化,学习 FPGA 电路的故障诊断方法,提升调试能力。

评论(0)